Nova tecnologia de chips elimina saliências de solda

[Imagem: Institute of Science Tokyo]

Sem saliências de solda

Uma nova tecnologia de fornecimento de energia para chips integrados em 3D promete ajudar a indústria a atender às demandas de aplicativos de computação de alto desempenho, que exigem alta largura de banda de memória, baixo consumo de energia e a quase supressão do ruído induzido pela fonte de alimentação.

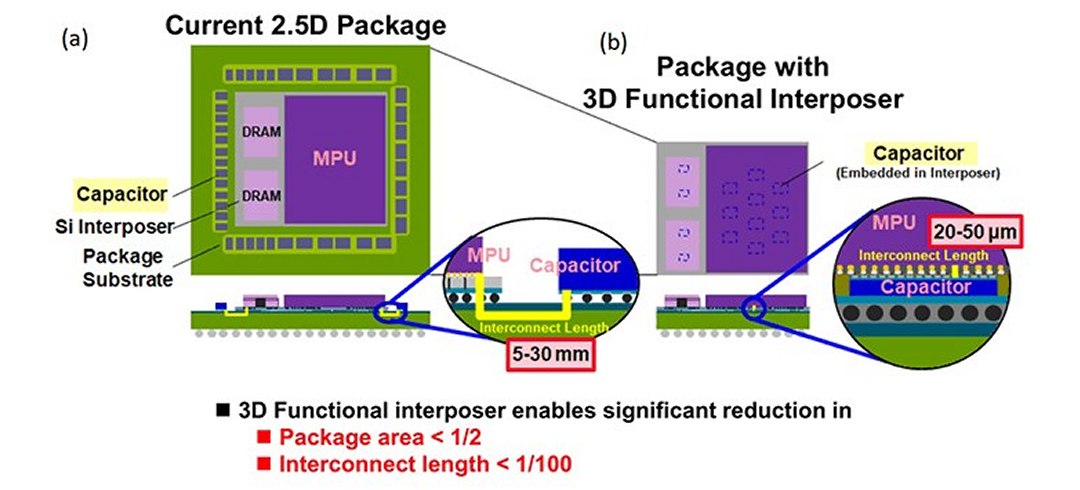

A abordagem tradicional de integração, conhecida como sistema em pacote (SiP: system-in-package), na qual chips semicondutores são dispostos em um plano bidimensional (2D), presos pelas tradicionais saliências de solda, apresentam entraves à miniaturização. Por isso, uma equipe do Instituto de Ciência de Tóquio, no Japão, criou um conceito inovador de integração de chips 2,5D/3D, que eles batizaram de BBCube, um acrônimo para “cubo de construção sem saliências”.

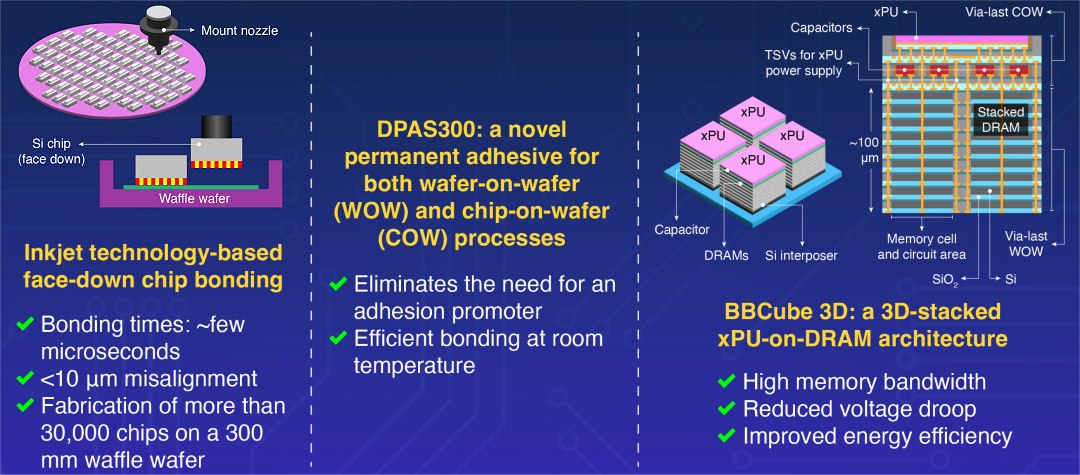

É essencialmente uma nova arquitetura de computação tridimensional empilhada, composta por unidades de processamento ou gráficas (xPUs) posicionadas diretamente acima das células DRAM (memória dinâmica de acesso aleatório). É um salto em termos de utilização prática em relação à técnica de integrar processador e memória em 3D, apresentada pela equipe há cerca de dois anos. Mas, para empilhar tudo, a equipe precisou desenvolver tecnologias-chave, envolvendo técnicas de colagem precisas e de alta velocidade, além de uma nova tecnologia adesiva.

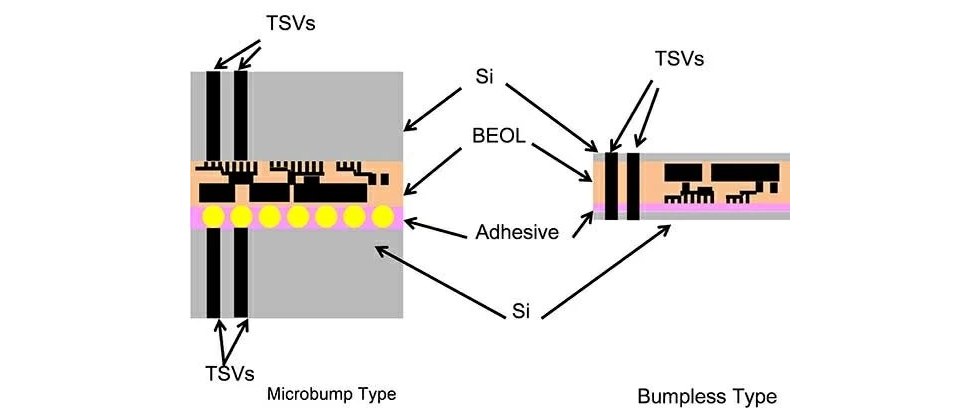

Tudo começa com um processo de chip sobre pastilha em uma configuração invertida, com a face para baixo, para contornar as limitações do uso das interconexões de solda, que resultam nas saliências. Utilizando tecnologia de jato de tinta e um método de revestimento adesivo seletivo, a equipe conseguiu fazer uma colagem sequencial de diferentes tamanhos de chip em uma pastilha de 300 mm de diâmetro, com um espaçamento muito estreito (10 micrômetros) e um tempo mínimo de carregamento de montagem (menos de 10 milissegundos).

“Mais de 30.000 chips de vários tamanhos foram fabricados na pastilha, alcançando uma alta velocidade de colagem sem nenhuma falha de descolamento do chip,” disse Norio Chujo, um dos idealizadores da técnica.

[Imagem: Institute of Science Tokyo]

Energia e ruído térmico

Para alcançar essa precisão e velocidade, a equipe precisou lidar com questões de estabilidade termal, que podem afetar o empilhamento multinível de pastilhas ultrafinas. Para isso, eles desenvolveram um novo material adesivo multifuncional, chamado “DPAS300”. Composto por uma estrutura híbrida orgânico-inorgânica, o novo adesivo demonstrou fortes adesividade e resistência ao calor durante os testes experimentais.

Por fim, para alcançar alta largura de banda de memória e melhorar a integridade de energia, os cientistas empregaram uma arquitetura 3D do tipo xPU-sobre-DRAM, reforçada por uma nova rede de distribuição de energia. Isso incluiu a incorporação de capacitores entre a xPU e a DRAM, a implementação de camadas de redistribuição na pastilha e a colocação de vias de silício nas pistas da pastilha e nas linhas de marcação da DRAM.

[Imagem: Institute of Science Tokyo]

Próxima geração de chips

“Essas inovações reduziram a energia necessária para a transmissão de dados de um quinto a um vigésimo da energia dos sistemas convencionais, além de suprimir o ruído da fonte de alimentação para menos de 50 mV,” destacou Chujo.

Se adotada pela indústria, essa arquitetura de computação empilhada 3D tem potencial para transformar os computadores e outros dispositivos eletrônicos da próxima geração.